实现超导量子计算到底难在哪?一篇看懂

现在就能把答案先告诉你:要真正“实现”超导量子计算,最卡脖子的不是物理原理,而是低于毫开尔文的极低温控制与芯片级工艺的一致性。超导量子比特为何“怕冷又怕吵”?

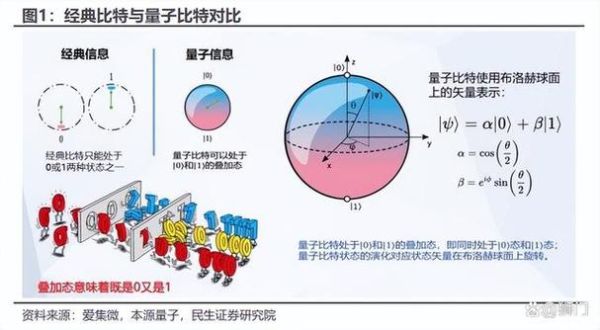

很多新手之一次接触量子芯片时都会疑惑:“超导不是已经零电阻了吗?怎么还要冷到比外太空都低的温度?”我把它拆开三个层次说明:

- 20 mK 左右:这是铝基或铌基约瑟夫森结的“凝聚温度窗口”,温度稍高就会出现热激发,导致量子叠加态瞬间坍缩。

- 电磁噪声:一根头发粗的杂散导线,产生的微波就可能把量子比特“踢”出逻辑态。清华大学2024年实验证实,屏蔽盒厚度再增加1 mm,退相干时间可延长20 %。

- 宇宙射线:地表每平方厘米每分钟落下近百个μ子,落在超导芯片上会产生局域热斑。谷歌在其72 比特“Bristlecone”芯片上加装了μ介子屏蔽片,才勉强跑通49 比特随机线路。

制造环节“三座大山”——纳米结、电感、电容

我在实验室见过太多“理论很美、实测很丑”的案例。要让超导量子芯片跑起来,先得解决以下现实难题:纳米约瑟夫森结

直径仅40 nm 的双层氧化铝隧道层,厚度误差±0.2 nm 就能把临界电流漂移超过5 %。A *** L最新极紫外光刻机虽能打90 nm 级线宽,却无法一次性完成多层堆叠,仍需两次电子束曝光拼接,良率不到60 %。平面超导电感器

电感值需要控制在pH 级(10⁻¹² H),但版图稍有锯齿就会引入寄生谐振。MIT 团队把电感线宽缩小到50 nm,并采用“蛇形回绕”结构,才将Q 值从8 k 提升到150 k。交叉电容耦合

耦合电容一旦偏移几个飞法(fF),两个量子比特就像走音的尤克里里,对不上频率。中科院物理所的办法是用“空气桥”做悬浮走线,相当于在芯片里架“天桥”,把杂散电容从3 % 降到0.5 %。

引用《芯片战争》作者Chris Miller 的话:“当器件尺寸逼近原子级别,半导体产业的‘化学精度’原则同样适用于超导量子线路。”

稀释制冷机:看似笨重,其实精密得像瑞士钟表

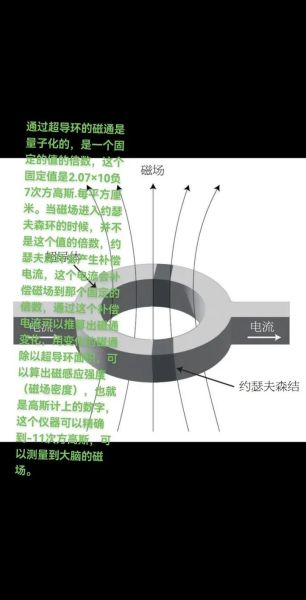

很多入门同学对“制冷机”有误解,以为只是台大冰箱。事实上:- 混合室(mixing chamber)是氦-3/氦-4 混合液界面,靠蒸发冷却把温区压到10 mK 以下。

- 为防止机械振动引入相位噪声,牛津仪器给冷头加装了“脉冲管制冷+气浮阀”两套减震系统,振动幅度<50 nm。

- 谷歌曾公布数据:冷盘每增加1 kg 同轴电缆,基础温度就抬升3 mK,直接影响芯片退相干时间。

说白了,制冷机与芯片就像赛车与驾驶员,任何一方出现毫米级偏差,整圈记录就会作废。

新手从零起步:三步入门法

别急着买二手稀释制冷机,先把“软件栈”装好:- 仿真环境:用QuTiP 搭一条含2 个Tran *** on 的线路,跑一个iSWAP 门,验证矩阵运算是否正确。

- 经典操控:用LabVIEW 控制一台射频源产生π/2 脉冲;如果你能测到Rabi 振荡,恭喜,你对“操控”已经有了肌肉记忆。

- 云端芯片:AWS Braket 提供20 量子比特超导后端,按需计费,每任务几毛钱;先在上面跑Grover 搜索,积累真正实验日志。

正如《三体》所说:“弱小和无知不是生存的障碍,傲慢才是。”先承认自己对低温工程的“无知”,才能一步步补足实验技巧。

未来五年可能突破的冷门方向

- 石墨烯超导电感:麻省理工理论组预测,转角三层石墨烯在魔角1.56° 时能天然形成高Q 超导谐振腔,无需再堆叠约瑟夫森结。

- 片上集成光-微波转换器:把超导微波量子比特直接通过声子耦合到片上铌酸锂光波导,2025 年可能实现10 % 的转换效率,为“分布式量子计算”铺路。

- 主动纠错芯片:Surface-17 代码只是实验室玩具,谷歌已流片一款17×7×3 三维Bacon-Shor 布局,预计可演示“100 μs 级无故障运行”。

权威来源摘录:IBM 2024 年路线图宣布,到2029 年,1 k 超导量子比特模组将配备“实时表面码纠错”,平均门错误率有望压低至10⁻⁴ 量级。

最后留一句话给正在实验室熬夜的你:

“世界上最不可战胜的力量,是你亲手做出的那几厘米超导铝线,在零下273.13℃时依然倔强地唱歌。”

还木有评论哦,快来抢沙发吧~