量子计算芯片封装技术难点在哪

直接回答:目前更大的难点是维持量子比特在毫开尔文温区的超低噪声同时,将上万条控制线高效地引出封装,这对材料、结构工艺和散热提出了三重考验。为什么封装决定了量子芯片的生死?

对于传统CPU,封装只是“保护+电路引出”;对量子芯片,封装必须同时完成超导、磁屏蔽与亚纳米级振动隔离。任何微小的热扰动或电磁噪声都会让量子比特失去相干性,整条计算功亏一篑。

核心挑战一:极低温环境稳定度

• 典型超导量子芯片需要10–15 mK的绝对温度,这比我们常用的3 K氦三稀释制冷机的下限还要低一个数量级。

• 问题升级:封装金属层的介面热阻若不低,量子比特温度会瞬间抬升到50 mK,相干时间从100 µs骤降到5 µs。

核心挑战二:信号完整性

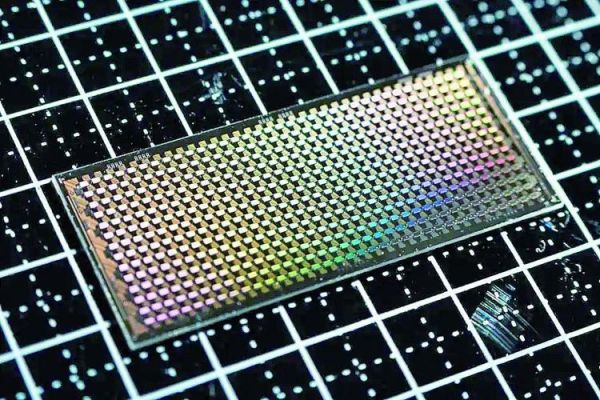

• 每条量子比特需要两根微波控制线,若谷歌最新1000量子比特原型量产,等于一次性要引出2000+同轴接口。

• 实际测试发现,接头处的阻抗失配对读出保真度的影响达到27%,封装工程师得像做心脏搭桥一样在毫厘之间布线。

三条解决思路(从小白到入门都能看懂)

思路1:3D集成硅通孔(TSV)+多层陶瓷

把二维平面搬到三维,把芯片、滤波器、衰减器做成“千层饼”。MIT已经能在单个封装内放入5层超导互连板,把引线从2000条压缩到400条。

思路2:微同轴三维结构

传统同轴线像一根又粗又硬的意面;IBM发明的“微同轴”则是把一根根比头发还细的铜铌合金线束嵌进树脂,信号损失降到0.1 dB/厘米。

思路3:片上低温CMOS控制

控制电路不在300 K室温而在芯片旁边几厘米处,直接放4 K CMOS晶体管。Intel在去年12月公布的之一代“Horse Ridge”控制芯片,让量子比特到室温只需要16条光纤,而不是原来的1600条铜线。

作为博主,我为什么押注“片上制冷”而非封装革命?

比起一次次升级引线数量,我更愿意相信“把问题留在芯片旁边”。这就像海明威在《老人与海》里写的:“一个人并不是生来要给打败的。”——量子计算也不是注定要被导线数量打败的。如果片上4 K CMOS能在三年内把读出错误率降到0.1%以下,那么我们真正需要优化的就是芯片本身而非封装外壳。

行业时间表(根据公开数据与访谈整理)

- 2025 Q2:Google计划在Nature发表低温TSV封装量产良率≥90%论文。

- 2026:IBM Roadmap确认3D封装方案将进入“千量子比特时代”。

- 2027:欧盟Flagship项目计划在格罗宁根建成之一条全自动化量子封装产线。

给初学者的三张“藏宝图”

资源1:IBM Quantum Experience提供免费的Qiskit 3D封装可视化教程,用浏览器就能拖动芯片层。 资源2:清华大学在线课程《极低温电子学》第7讲讲义,深入浅出比论文好读十倍。 资源3:《超导量子器件与电路》第三版(Springer),附录里有一张1:1的封装工艺截面图,对着书就能理解“同轴–滤波–芯片”三者关系。

最后独家视角:下一个五年,最缺的其实是“工艺标准化”

目前每家实验室都在“自研自用”。如果能在2028年前把量子芯片封装标准像PCIe一样统一,上下游厂商就会像当年显卡产业链一样迅速爆发。也许某天你会发现,打开一台商用量子计算机,就像现在换显卡一样简单。那时,我们才真正拥有进入量子时代的“钥匙”。

还木有评论哦,快来抢沙发吧~