超导量子计算测控系统入门

是测控系统到底是什么?

超导量子芯片就像刚出生的小猫咪,极怕冷、怕吵,也怕陌生人乱碰。测控系统就是那个高级“育婴师”,它负责给芯片输送微波脉冲、测量回波,再把数据处理成我们能看懂的“量子比特状态”。我之一次在低温实验室看到一排排金色同轴线时,心里直犯嘀咕:这跟家里的路由器有啥区别?后来师兄告诉我,区别大了——路由器的信号要是掉一格,大不了视频卡顿;测控系统里要是掉一格,整片芯片就可能“塌缩”成废数据。

(图片来源 *** ,侵删)

三大核心模组各司其职

- AWG任意波形发生器:相当于“发音器官”。它把指令翻译成极短的微波脉冲,脉冲宽度可到0.1纳秒以下,时间精度堪比奥运会百米计时。

- 数字化采样仪:扮演“耳朵”。它需要把从芯片反射回来的百万级波形,在50毫开尔文下无损地放大到伏特级,同时保持相位完整性;这种放大器常被称作HEMT低噪声放大器。

- FPGA实时处理板:是“大脑”。它把采样数据实时做FFT、阈值判断,再把结果丢给上位机,整个过程延迟控制在微秒级以内。

“温控”为何比“测控”更先发生

量子芯片需要在20毫开尔文以下工作,否则热噪声会直接淹没量子态。这相当于让你在大风里听蚊子扇翅膀。实验室常用四级降温:- 室温→40 K(脉冲管制冷机)

- 40 K→4 K(氦-4壶)

- 4 K→0.8 K(氦-3壶)

- 0.8 K→20 mK(混合稀释制冷机)

每一级都要插入低通滤波与红外遮挡,否则外部辐射足以杀死量子相干性。就像《孙子兵法》说的“立于不败之地而不失敌之败也”,先让系统“冻住”,才能谈后续探测。

微波脉冲如何读写量子比特?

超导比特多数是Tran *** on(传输子)结构,能量级差落在5–7 GHz。• 写入:AWG发射一个包络调频微波,把|0⟩激励到|1⟩,相当于对经典比特敲“SET”命令。

• 读取:比特腔耦合会移动谐振频率,数字化仪测频移即可映射量子态。此时必须保证“量子非破坏性”,即读一次不能直接把|1⟩读成|0⟩。

我踩过的坑:误把脉冲时长当成相位主因,结果相干时间从100微秒跌到30微秒;后来才发现是门波形里微小的泄露电容导致。提醒新手,别迷信仿真,一定要实测眼图!

量子误差纠错需要怎样的测控速度?

传统服务器出错概率约十亿分之一;量子比特出错概率却只有千分之一。为了千分之一降到十亿分之一,必须实时监控并实时纠错。这就要求:• 单周期时间 < 比特退相干时间(约100 μs)

• 并行通道数 > 比特数×纠错层数(通常每个物理比特配3–5个校验比特)

据IBM 2023路线图披露,下一代“Heron”处理器需要至少五千条独立微波通路,而现阶段更好的商用系统只能做到几百路。行业正在尝试光电混合或RF-SoC单芯片方案,把AWG、ADC、FPGA全塞进一片硅里,降低延迟、缩小体积。

个人实战小贴士

之一,用示波器先看“形状”,再上低温。在室温下调好波形,可以省去在液氦里拆装线缆的痛苦。第二,把数据流拆成“批-帧-包-字节”四层。FPGA里逐级缓存,避免突然的数据瀑布导致内存溢出。

第三,留一条常开“调试口”。我曾在芯片失相后,通过这条口连续打低功率探测脉冲,成功复现了相干塌陷的全过程。若没有这条通道,只能把芯片提上来常温再测,浪费两天时间。

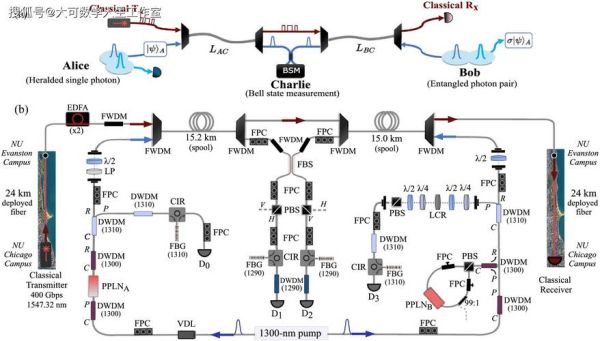

(图片来源 *** ,侵删)

引用资料:Barry Sanders《量子信息基础》、IBM Quantum Network Roadmap 2023、《热力学与统计物理,张启仁》

(图片来源 *** ,侵删)

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~