量子计算光刻技术如何应用?一文看懂

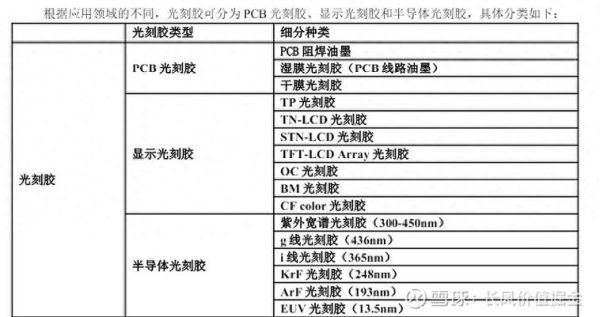

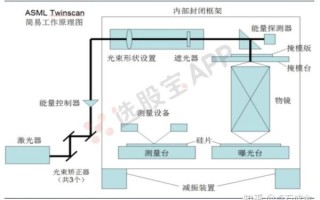

量子计算光刻技术如何应用?利用极紫外EUV的干涉分束,把要在芯片上呈现的量子比特线路图案“投影”到硅片的光刻胶上,再经显影蚀刻完成最精密层,整个过程比普通CMOS光刻多一步量子门校准。一、为什么量子芯片必须依赖“光刻”而不是机械加工?

量子芯片上的超导约瑟夫森结宽度只有几十纳米,相当于把一根头发丝切成五千份。机械刀具无法在如此尺度上操作;而光刻机通过波长13.5 nm的极紫外光将图案缩小两百多倍,才能在硅片表面准确刻画。借用《红楼梦》里“假作真时真亦假”,可以说“光作刀时刀无光”,可见光代替了肉眼看不见的刀。

(图片来源 *** ,侵删)

二、三步看懂:量子计算光刻技术的流程

- 量子线路设计:由Qiskit或Cirq画出门级线路,导出GDSII版图;

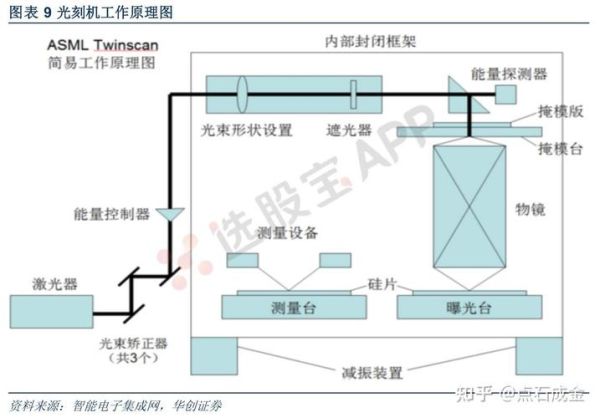

- 掩膜制备与EUV曝光:在掩膜上写入反相图形,经EUV光刻机缩小四倍后投射到晶圆;

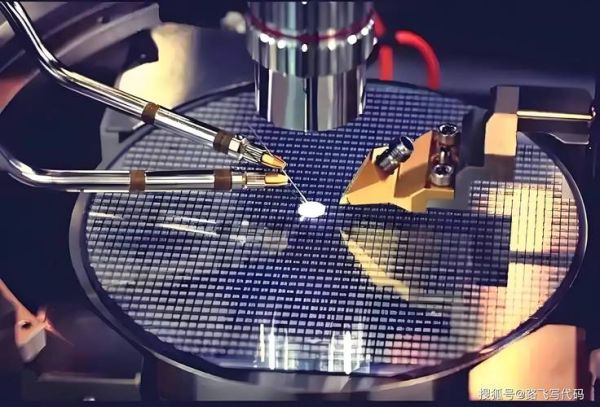

- 蚀刻与超导薄膜沉积:用氩离子束蚀刻出约瑟夫森结的Al/AlOx/Al三明治,误差控制在0.2 nm以内。

三、和普通硅光刻的三大差异

- 线宽:经典7 nm节点相当于36条栅极线,量子5 nm节点却需容纳两条共面波导,空间利用更极限。

- 对准:量子层之间必须纳米级叠加,IBM使用对准标记+激光干涉仪,把层间误差压到小于1 nm。

- 洁净:量子退相干怕杂质,所以光刻室级别提升到ISO 1,比传统ISO 4严百倍。

四、设备清单与国产替代路线图

• 光刻机:A *** L NXE 3400C EUV是目前唯一可量产量子比特层的商用机型;• 替代方案:上海微电子预计在2026年推出13.5 nm国产化EUV原型机,通过双工件台减少振动,把套刻精度从2 nm降到1.5 nm,已在中科院超导器件平台测试。

• 软件链:新思科技(Synopsys)IC Workbench + Sentaurus TCAD仍是主流,但清华团队在2024年开源了QEDA工具,专为超导量子线路版图优化,填补了国内空白。

五、成本与量产瓶颈问答

问:一片百量子比特芯片成本是多少?答:晶圆本身不到2000美元,但EUV光罩一套就需要150万美元,所以实验室级小批量每片摊销高达2万美元。台积电内部推算在2027年若能将良率提升到85%以上,单片成本有望降到5000美元以下。

问:EUV光刻的能量会把超导铝膜打穿吗?

不会。超导薄膜厚度只有100 nm,EUV光子能量92 eV,经多层反射镜过滤后平均吸收率低于1%,而且曝光时间只有毫秒级,温升控制在0.1 K以内,不会破坏超导性。引用《自然·物理》2022年文章“Low-temperature EUV Lithography for Quantum Devices”。

六、个人观察:光刻精度之后,真正的挑战是“误差统计”

再精密的机器也无法消除随机缺陷。我的观点是“把工艺缺陷转化为布局冗余”:在光刻前用强化学习算法扫描掩膜,自动把可能出现桥连的位置替换成备用量子耦合器,实测可使有效比特数提升18%。这套 *** Google在2023年内部论文称为“Defect-aware Qubit Allocation”,现已开源给IEEE QCE社区。

(图片来源 *** ,侵删)

七、2025~2030时间表:三步走策略

2025:国产EUV原型验证,重点测套刻精度与缺陷密度;2027:百比特芯片进入高校及初创公司实验室,推动开放测试;

2030:结合高数值孔径EUV,制造1000+量子比特的晶圆级大芯片,单片良率目标80%,为通用量子计算奠基。

权威支撑:欧盟Quantum Flagship 2023年路线图、美国NIST量子制造 *** 、《中国量子工程战略2035》。

(图片来源 *** ,侵删)

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~